作業前の準備

この章では、Trenz社のサンプルプロジェクトをダウンロードし、その中にある必要なフォルダの説明と、bdファイルの生成方法について説明します。

また、SDSoC用のデザインのフォルダを構成する上での注意点を説明します。

必要なツール

このチュートリアルでは下記のツールを使用します。

サンプルデザインのダウンロード

Trenz社のWebサイトから、2017.1に含まれるzynqberrydemo1のprebuild版をダウンロードします。(zynqberrydemo2またはzynqberrydemo3でも構いませんが、2017.4版はNGです)

これを解凍します、

BDファイルの作成

SDSoCデザインのひな形を作るためにはbdファイル(BlockDesignファイル)が必要です。しかし、bdファイルはTrenz社のサンプルに含まれてはおらず、VivadoでTclスクリプトを実行して生成することになります。

bdファイルの作成にはVivado 2017.1~2017.4のいずれかが必要です。2018.1では

ERROR: [BD 5-216] VLNV

というエラーが出て生成できません。(XILINXのクロックウィザードのIPコアのバージョンが古いため、2018.1ではこのスクリプトを実行できない)

そのため、Vivado 2017.4以前を使いますが、わざわざファイル1つの生成のためにVivadoをダンロードするのが面倒だという方のために、生成したbdファイルを特電アーカイブの中に入れておきます。

bdファイルの作成は以下の手順で行います。

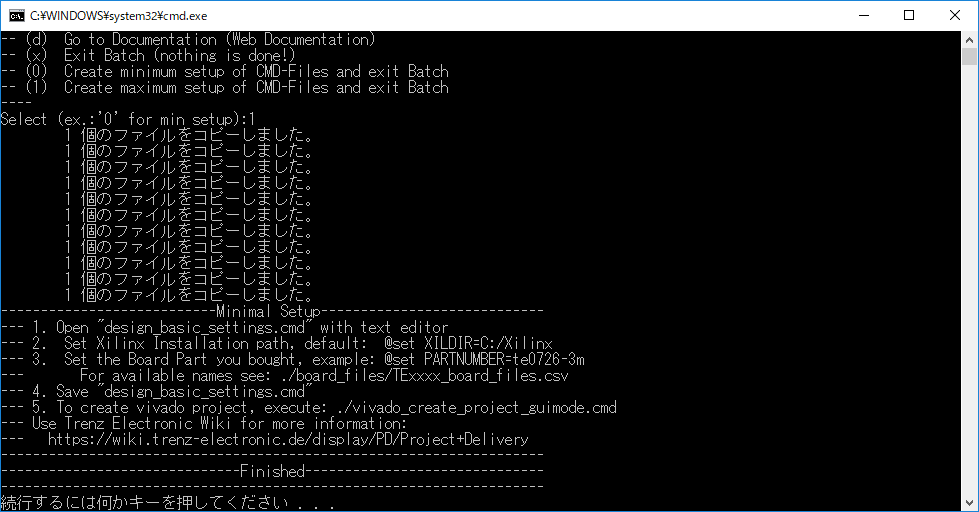

Trenzプロジェクトのzynqberrydemo1をダウンロードし、_create_win_setup.cmdを実行すると、

Select (ex.:'0' for min setup):

と聞かれるので、1を押してEnterを押します。

以下のように、cmdファイルがたくさん作られます。

design_basic_settings.cmdを編集します。

編集するべき項目は、

@set XILDIR=C:/Xilinx

@set VIVADO_VERSION=2017.1

@set PARTNUMBER=LAST_ID

@set SWAPP=NA

@set DO_NOT_CLOSE_SHELL=0

の各行です。

XILDIRはVivado 2017.4をインストールしたフォルダを指定します。

VIVADO_VERSIONにはVivadoのバージョンを指定します。

PARTNUMBERは3を指定します。

SWAPPはmybootとします。

DO_NOT_CLOSE_SHELLは1にします。

@set XILDIR=D:/Xilinx

@set VIVADO_VERSION=2017.4

@set PARTNUMBER=3

@set SWAPP=myboot

@set DO_NOT_CLOSE_SHELL=1

また、

@set ENABLE_SDSOC=0

の行は0のままで構いません。(変更しないでください)

それから、zynqberrydemo1\block_designフォルダのzsys_bd.tclを編集し、25行目の

set scripts_vivado_version 2017.1

を

set scripts_vivado_version 2017.4

に変更します。

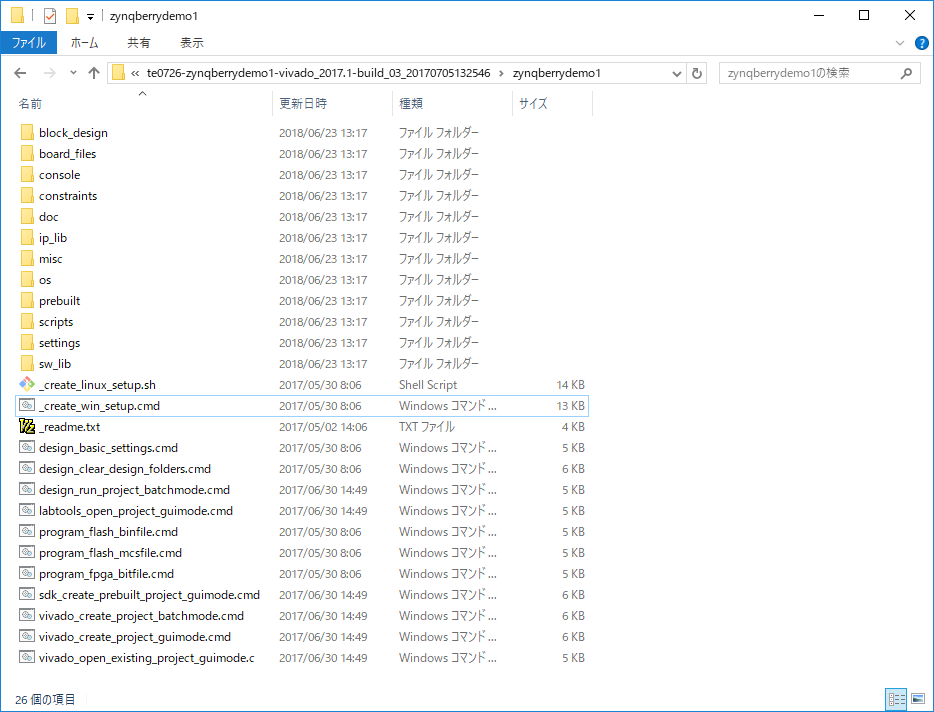

次に、バッチファイルのvivado_create_project_batchmode.cmdか、またはvivado_create_project_guimode.cmdを実行します。どちらも機能は同じで、DOSプロンプトで実行されるか、GUIで実行されるかだけの違いです。

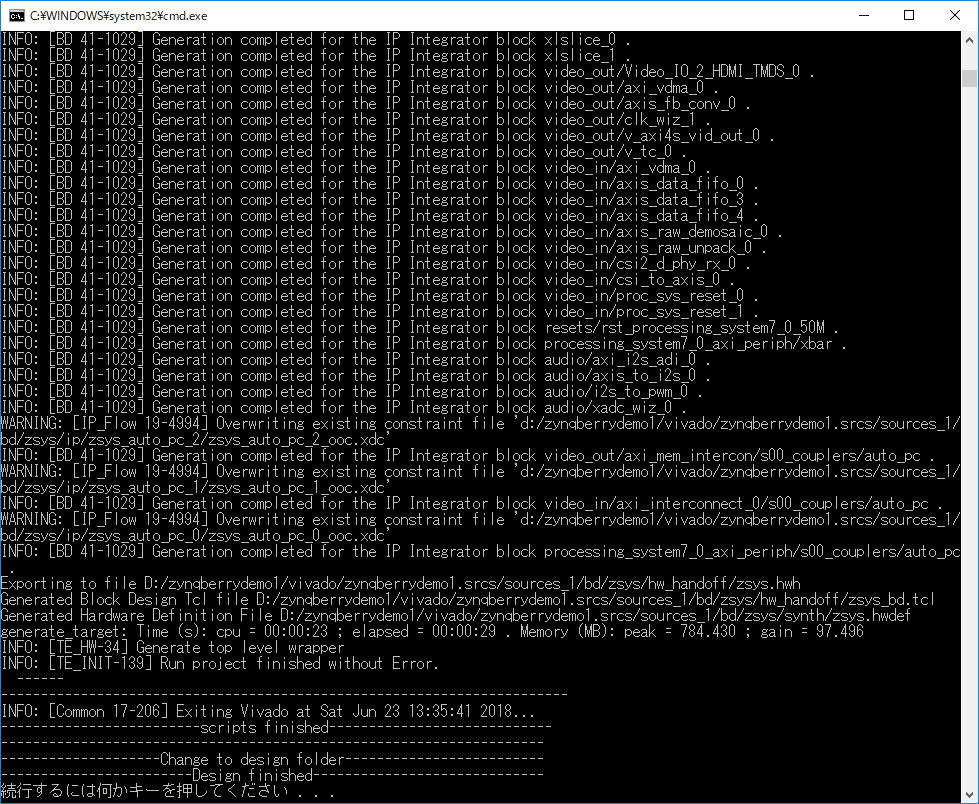

vivado_create_project_batchmode.cmdを実行した場合、DOSプロンプトが開き、vivadoフォルダが生成されます。

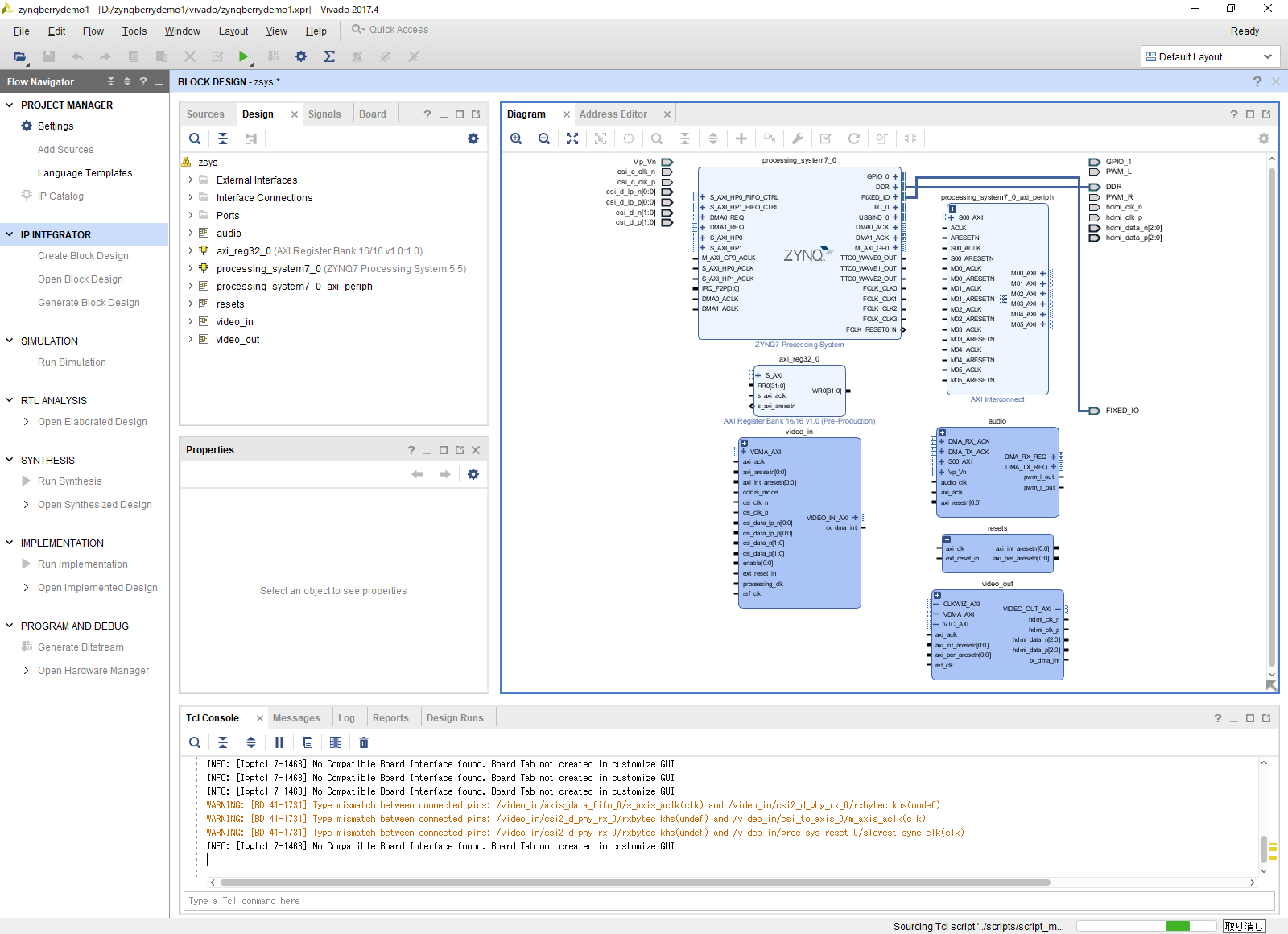

vivado_create_project_guimode.cmdを実行した場合は、Vivado上でさまざまなコンポーネントが置かれ、BlockDesignが追加されていくのが見えます。

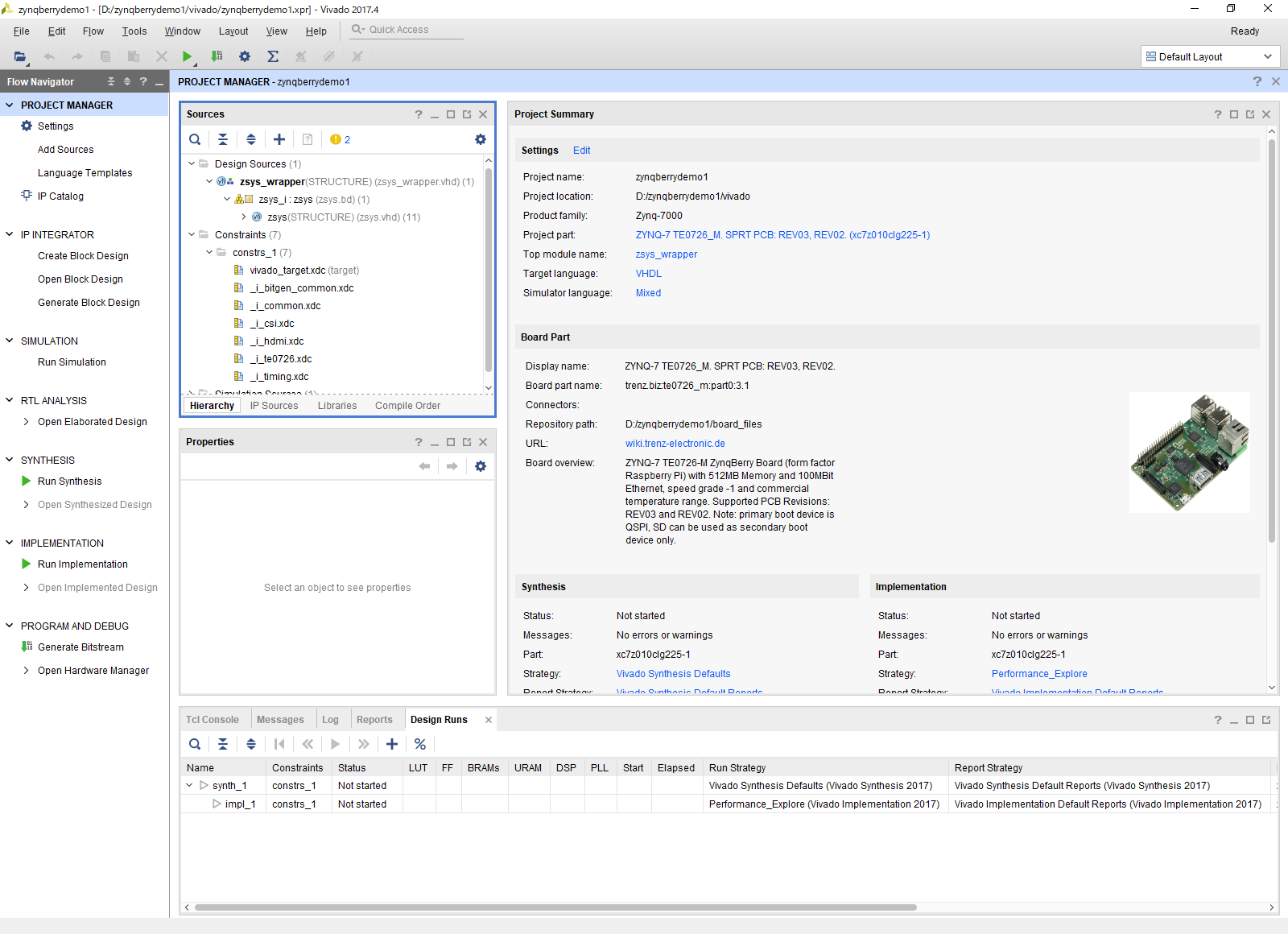

この手順で作られたVivadoプロジェクト自体は使用されず、必要なファイルは、

vivado\zynqberrydemo1.srcs\sources_1\bd\zsys\zsys.bd

のみです。bdファイルのサイズは306kBです。

もしエラーが出てで、設定を変えてやり直す場合は、design_clear_design_folders.cmdを一度実行してからバッチファイルを起動してください。

必要なファイルのコピー

SDSoCの環境はD:\SDSoCフォルダに作るものとします。

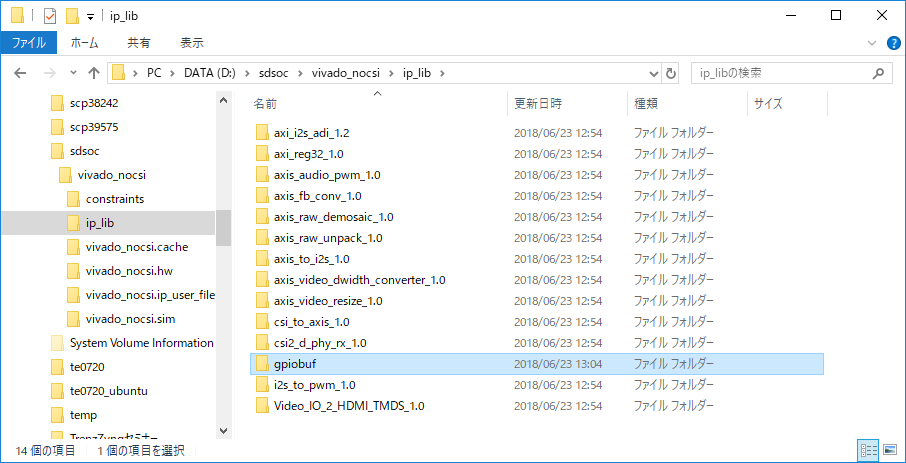

あらかじめ、エクスプローラでD:\SDSoC\vivado_nocsiフォルダを作り、その中にTrenzのサンプルプロジェクトにあるconstraints、ip_libフォルダをコピーします。

Trenz社のサンプルプロジェクトではip_libとvivadoフォルダが同じレベルにありましたが、この構成ではSDSoCはIPレポジトリを認識してくれません。必ず、Vivadoのプロジェクトフォルダの下にip_libフォルダとconstraintsフォルダが存在する必要があります。

また、ip_libフォルダにはgpiobufフォルダを特電アーカイブからダウンロードして入れておきます。gpiobufはVivado2017.3以降でTrenzプロジェクトを使うのに必要な追加のIPです。