元デザインの修正

Trenz社のサンプルプロジェクトの2017.1版のZynqberrydemo1~3は、Vivado 2017.3やSDSoC 2017.3以降で使用するときに様々なエラーを起こします。

このページではその対処方法を示します。

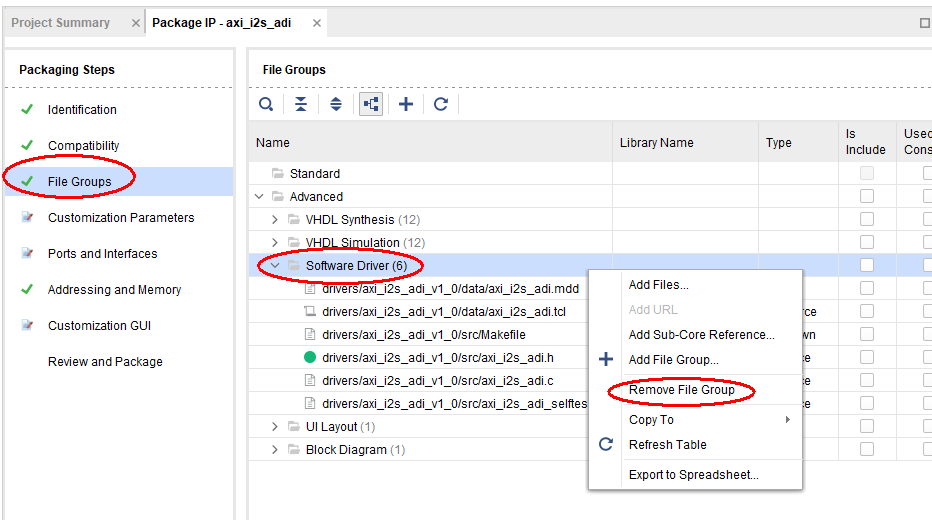

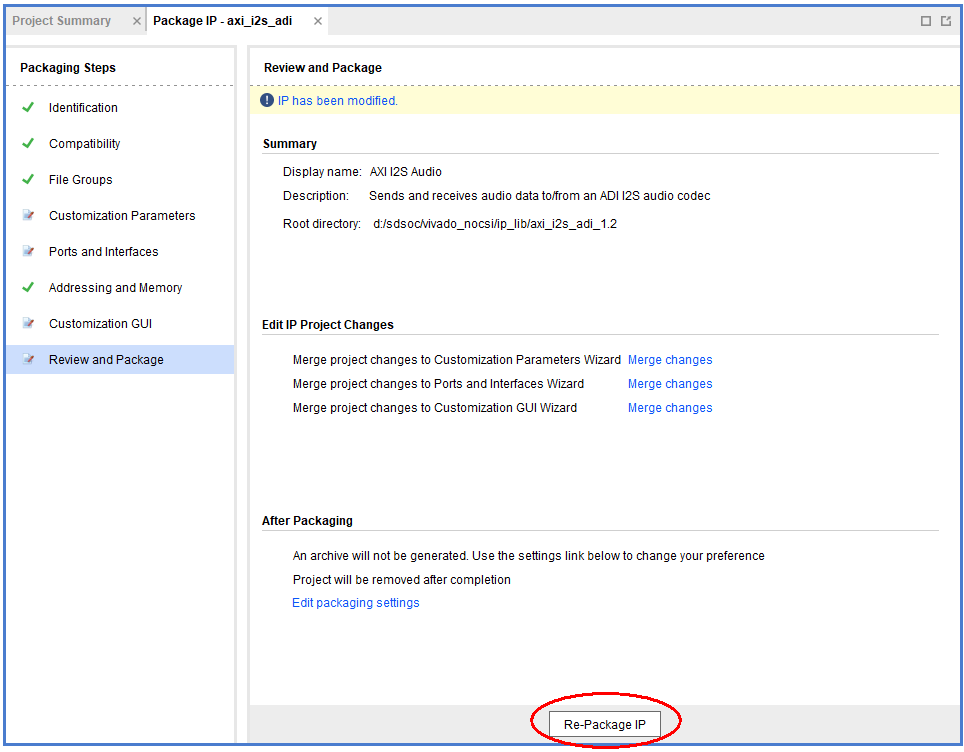

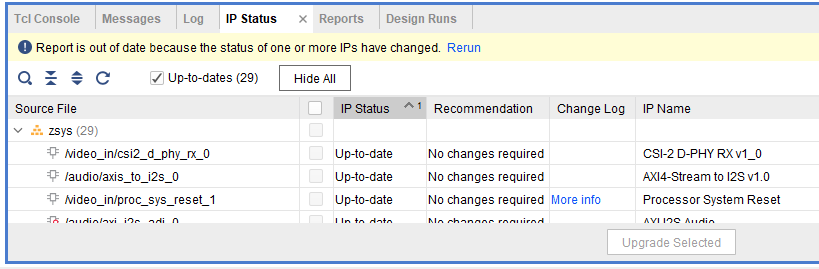

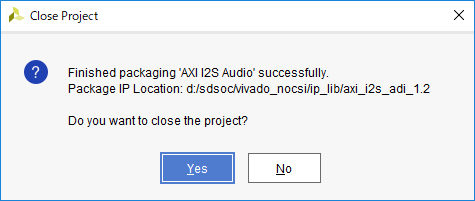

デバイスドライバの削除

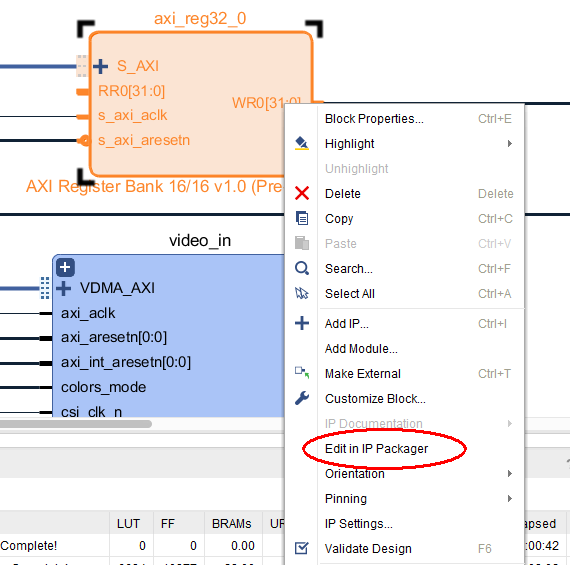

Block Designを開き、audioの中にあるaxi_i2s_adi_0を選択して右クリックし、Edit in IP Packagerで子プロジェクトを開きます。

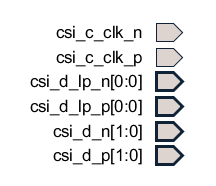

CSI入力の削除

Vivado 2017.3以降では、CSI入力回路がタイミングエラーを起こすため、削除します。

このタイミングエラーは微々たるものですが、XDCのset_falst_pathで消すことはできません。Vivadoで論理合成する場合は無視することができますが、SDSoCでは些細なタイミングエラーでも合成が止まってしまうため、ここではCSIモジュールごと削除することにします。

今後、VivadoやSDSoCのバージョンが上がった際には再び使えるようになるかもしれません。

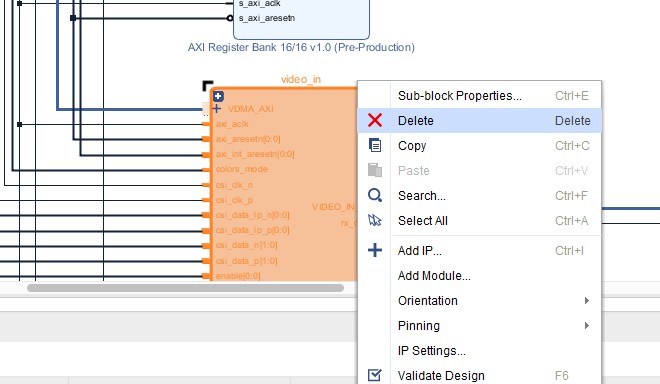

まず、video_inを選択し、DELキーを押すか、右クリックしてDeleteを行います。

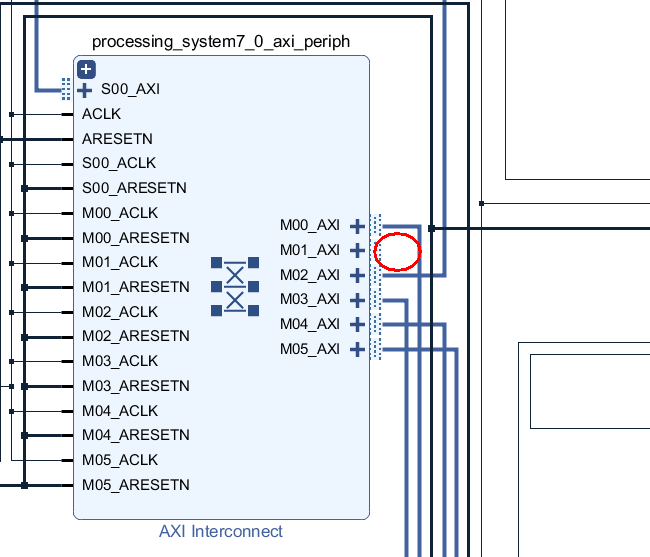

このように、AXI Interconnectに空きポートができます。

この状態で放置しておくと、AXI Interconnectの中がAXI Liteにならない(FULL AXIで作られる)ため、タイミング制約を満たすことができなくなって最終的にエラーとなってしまうため、空きポートを詰める処理をします。

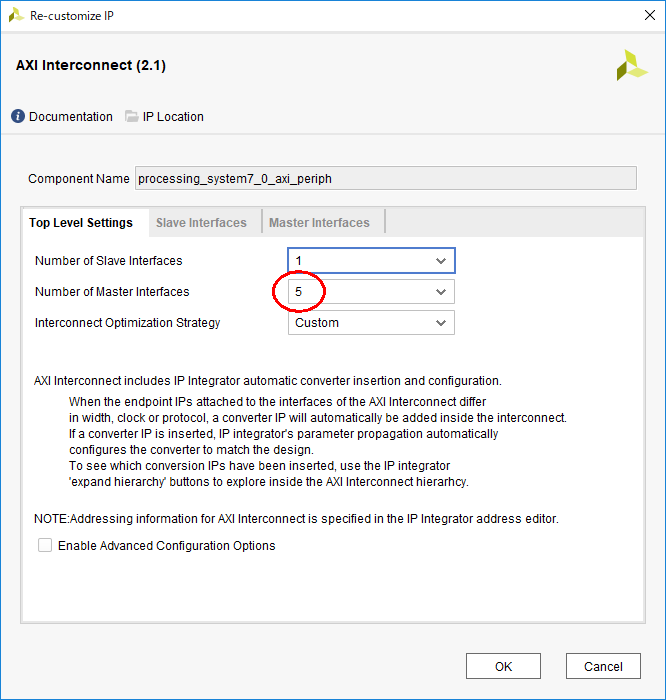

AXI Interconnectをダブルクリックし、開いたダイアログでMaster Interfacesの数を5にして、OKを押します。

これだとポートの数が変わってしまうので、

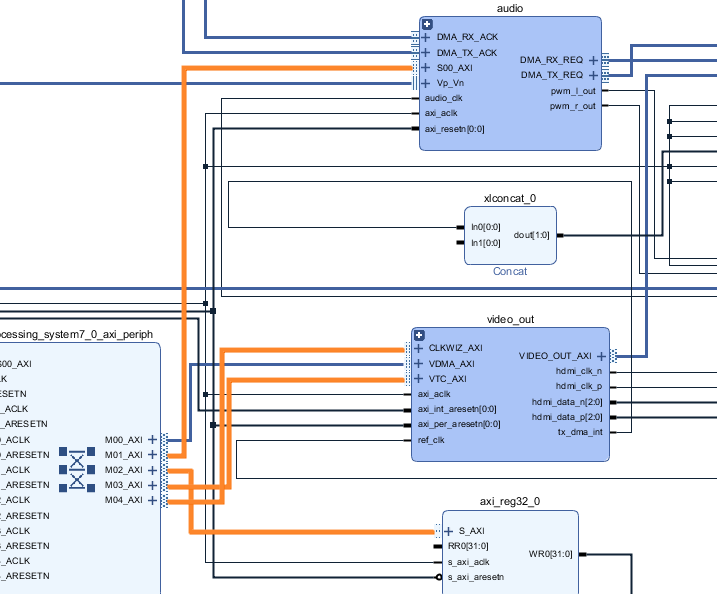

- AudioのS00_AXIをinterconnectのM01_AXIに

- axi_reg32_0のS_AXIをinterconnectのM02_AXIに

- video_outのVTC_AXIをinterconnectのM03_AXIに

- video_outのCLKWIZ_AXIをinterconnectのM04_AXIに

それぞれ、つなぎなおします。

残っているCSI入力を削除します。

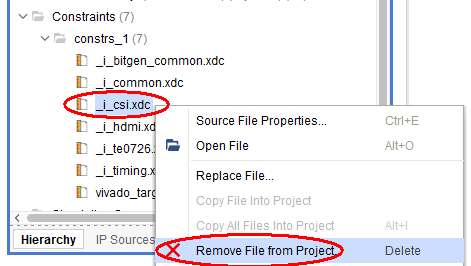

制約ファイルからも_i_csi.xdcを削除します。

これでCSI入力モジュールが安全に削除できました。

アドレスの再設定

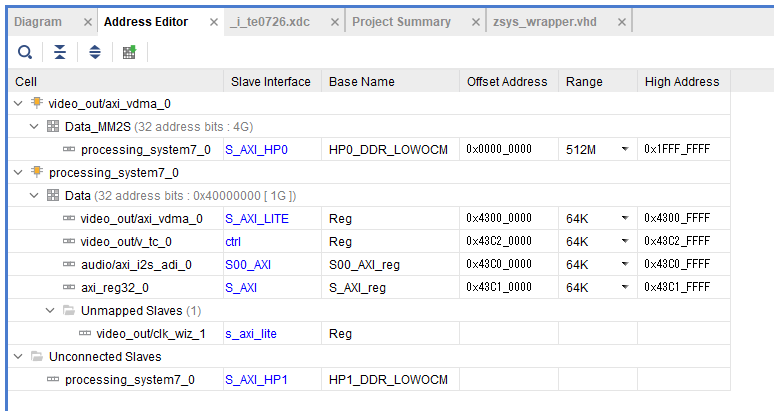

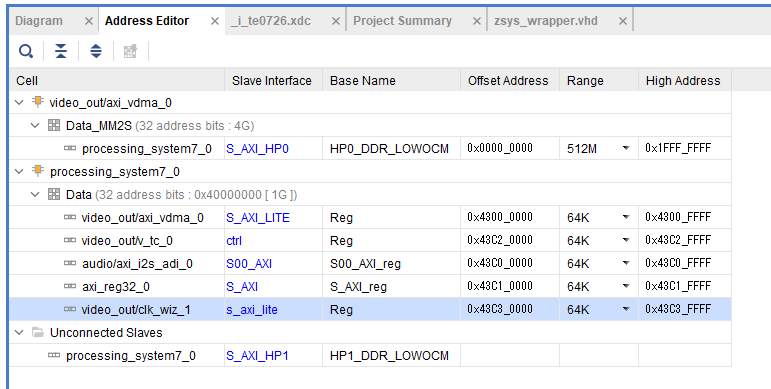

CSIモジュールを削除したり、AXIポートをつなぎ変えた関係で、アドレスがずれている場合があります。

Addressエディタを開いて、Umpapped Slavesがある場合は右クリックしてアドレスを設定しなおします。

GPIOバッファモジュールの追加

Vivado 2017.3以降ではPS7のGPIOをそのまま双方向ポートに出せないため、Block Designに特電ライブラリに入っているgpiobufモジュールを追加します。

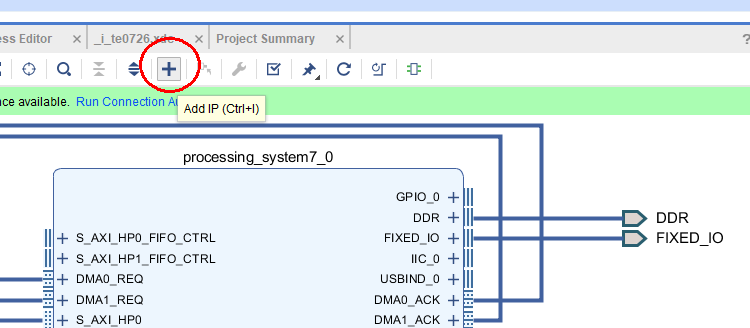

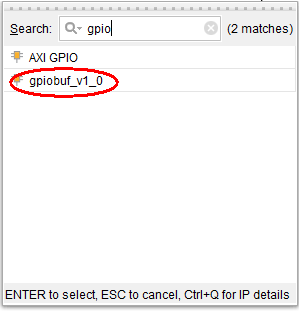

+ボタンを押して、Add IPを行います。

検索にgpioと入力すると、gpiobuf_v1_0というのが見つかるので、これを選択します。

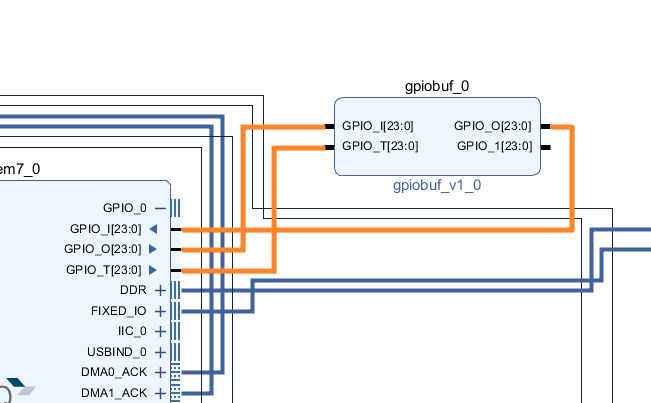

gpiobufモジュールが追加されるので、下の図のようにPS7のGPIO_0を開いて、GPIO_0の中の3つのバスをgpiobuf_0につなぎます。

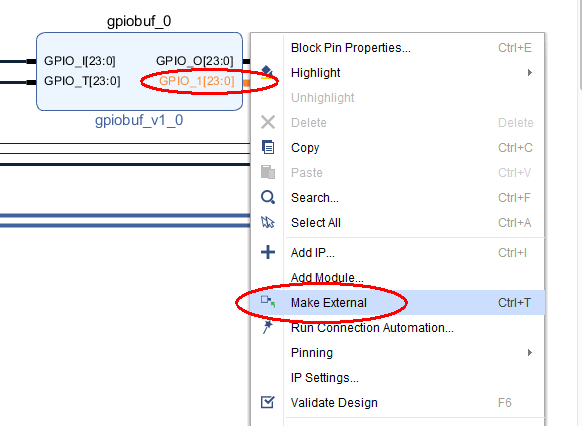

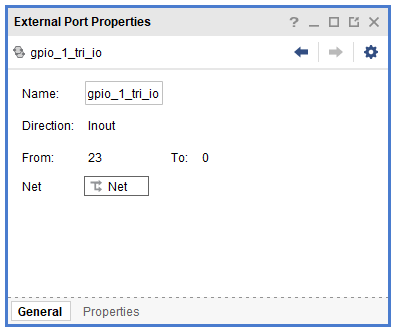

gpiobuf_0のGPIO_1ポートを選択し、右クリックして、Make Externalを行います。

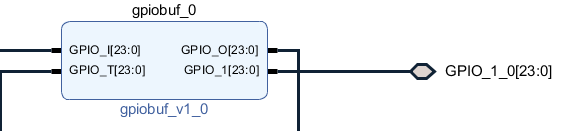

デフォルトでGPIO_1_0というポートが作られるので、このポートをクリックします。

Vivadoの画面にあるプロパティウィンドウで、名前をgpio_1_tri_ioに変更します。

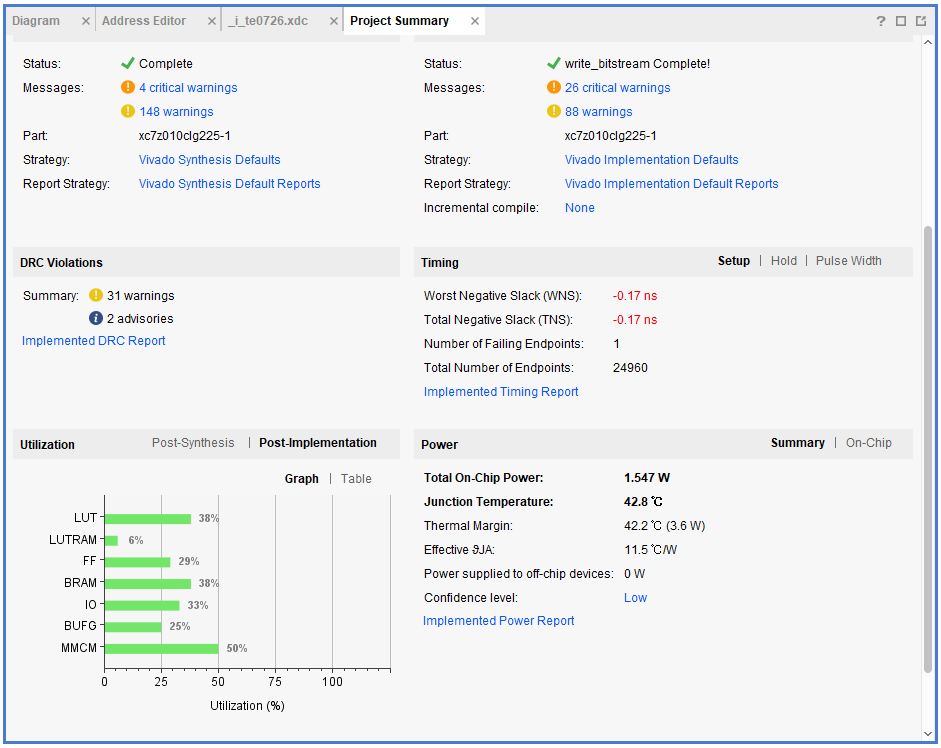

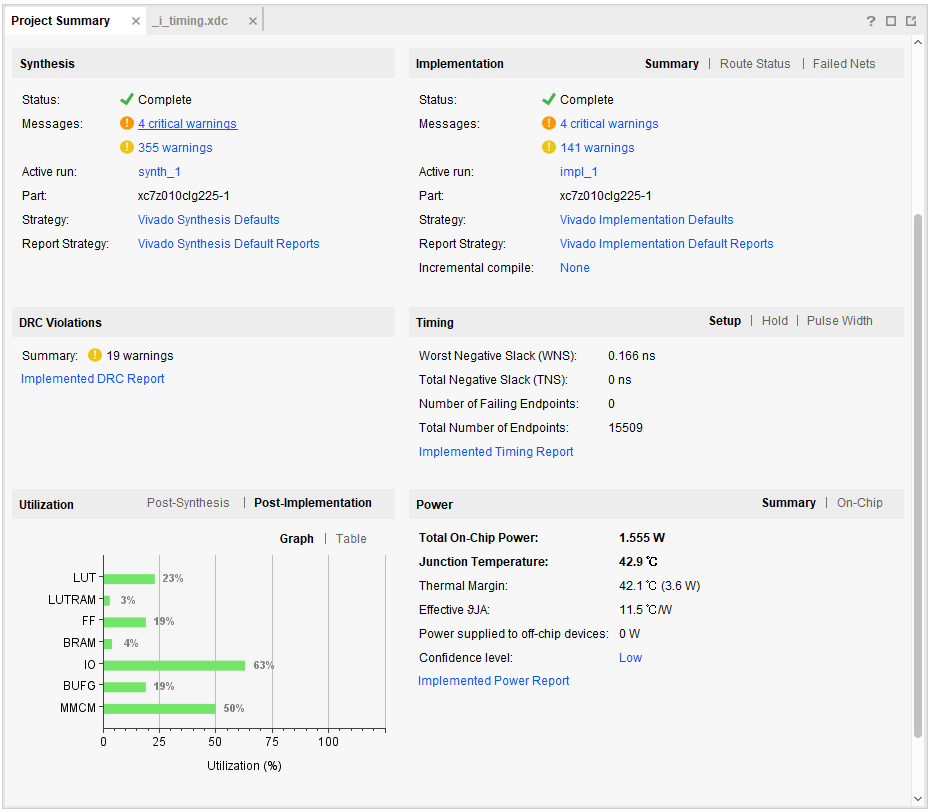

BitStreamを作ってみる

これでVivado 2018.1でも使えるZynqberrydemoのデザインができました。

一度保存して、Validate Design、Generate Output Productsを行って、Generate BitStreamを行ってみてください。

エラーを起こさずに論理合成が通るはずです。