元デザインの作成

この章では、Trenz社のサンプルプロジェクトを元に、クリーンな状態のVivado 2018.1用のプロジェクトを作成する方法を紹介します。

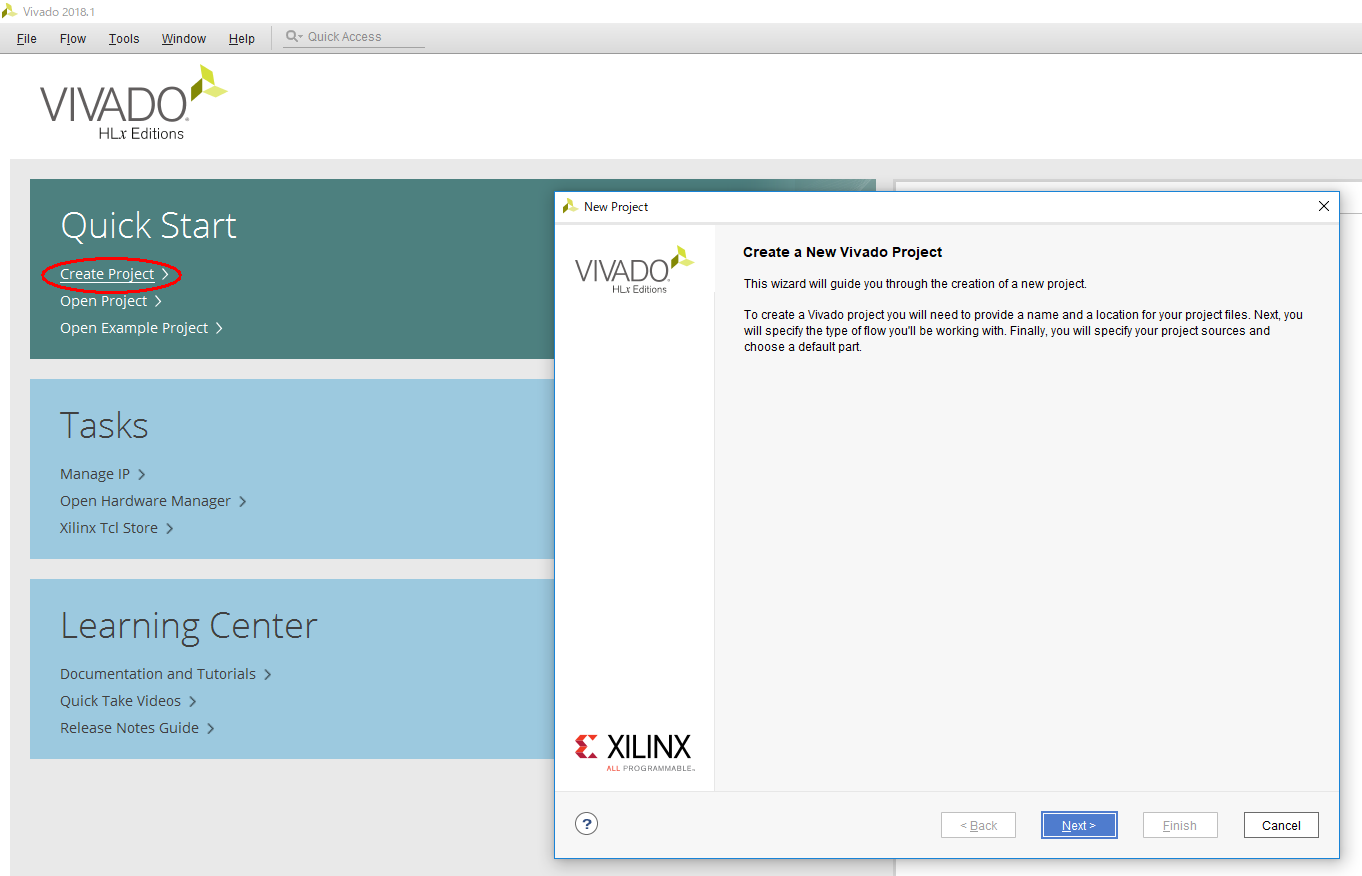

Vivadoプロジェクトの作成

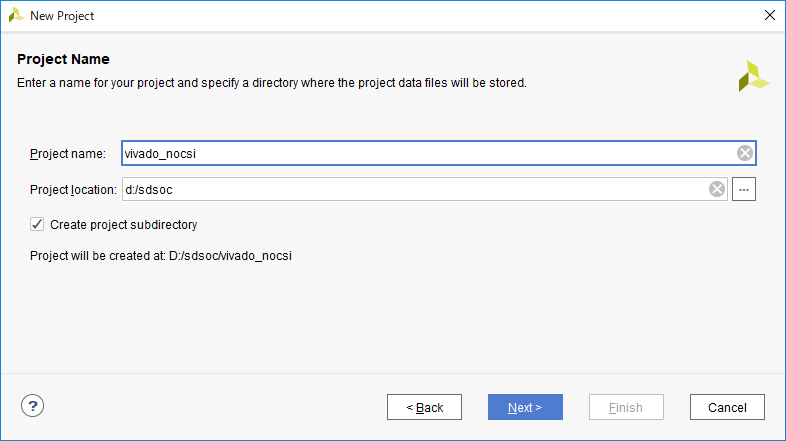

Vivado2018を起動して、プロジェクトを新規作成します。

プロジェクトのフォルダはD:\sdsoc\vivado_nocsiとします。理由は後述します。

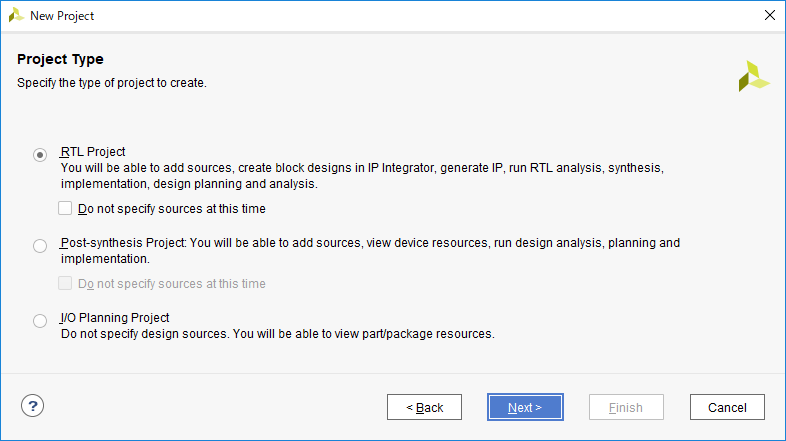

プロジェクトのタイプはRTL Projectを選びます。

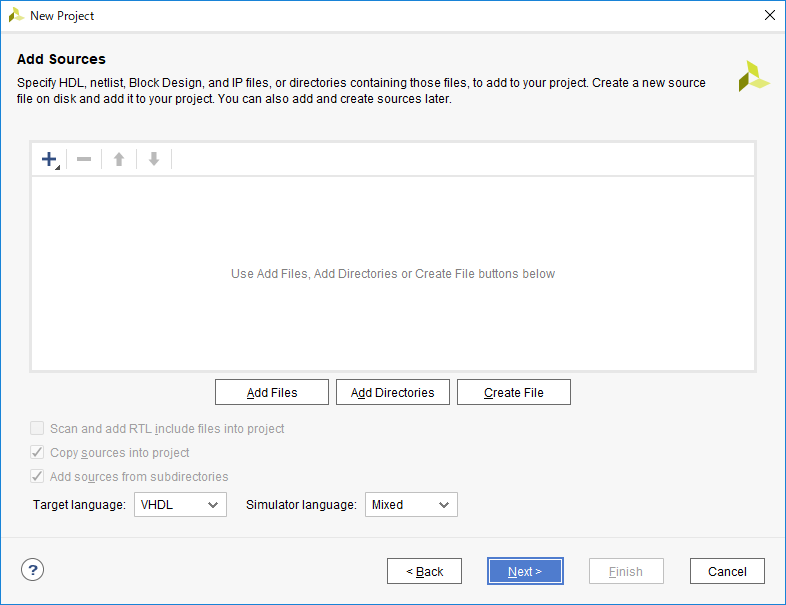

ここでは、Target languateをVHDLにするかVerilogにするか、好みのほうを選択します。

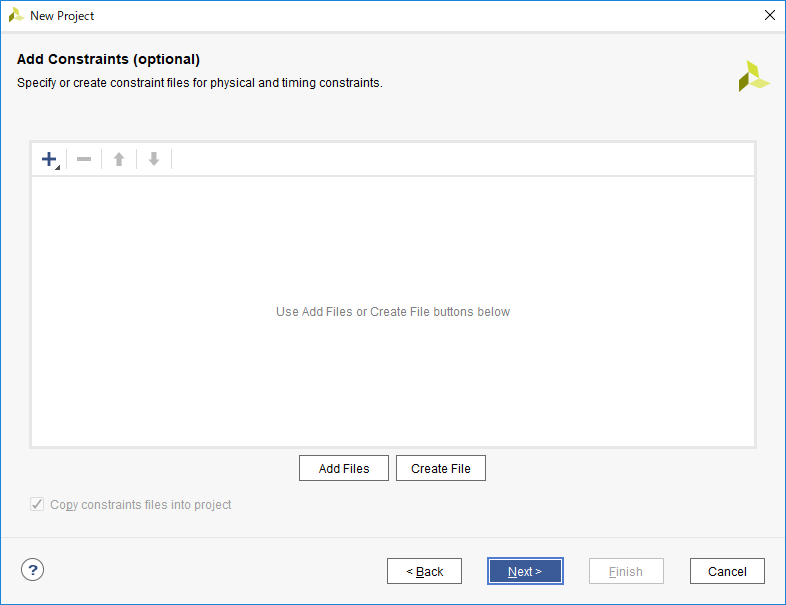

Add Constraintsでは特に追加するものはありません。Nextを押します。

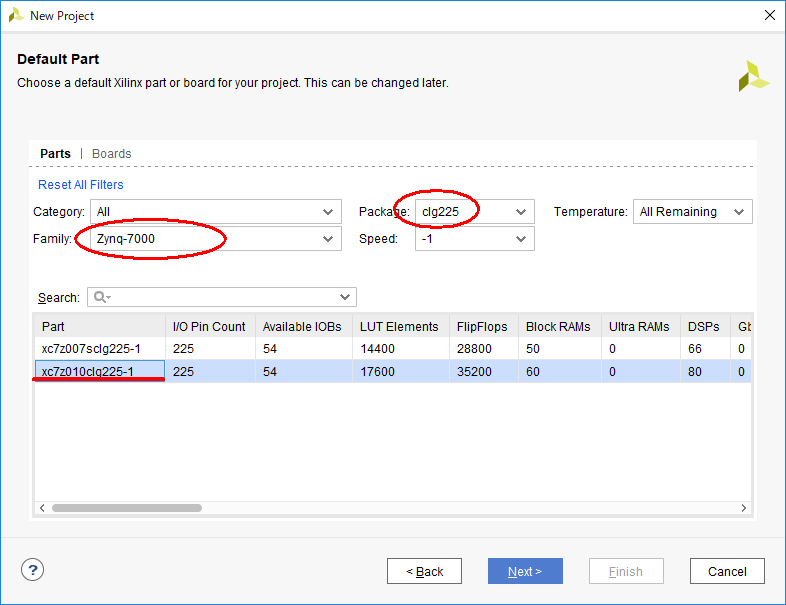

Partの選択はxc7z010cls225-1を選びますが、FamilyをZynq-7000とし、Packageをclg225とすると見つけやすくなります。

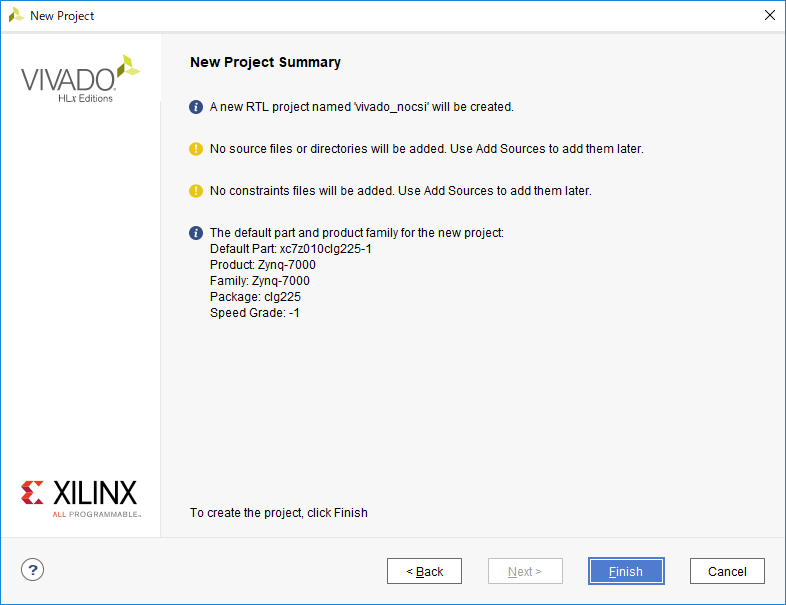

Finishを押します。

プロジェクトの設定

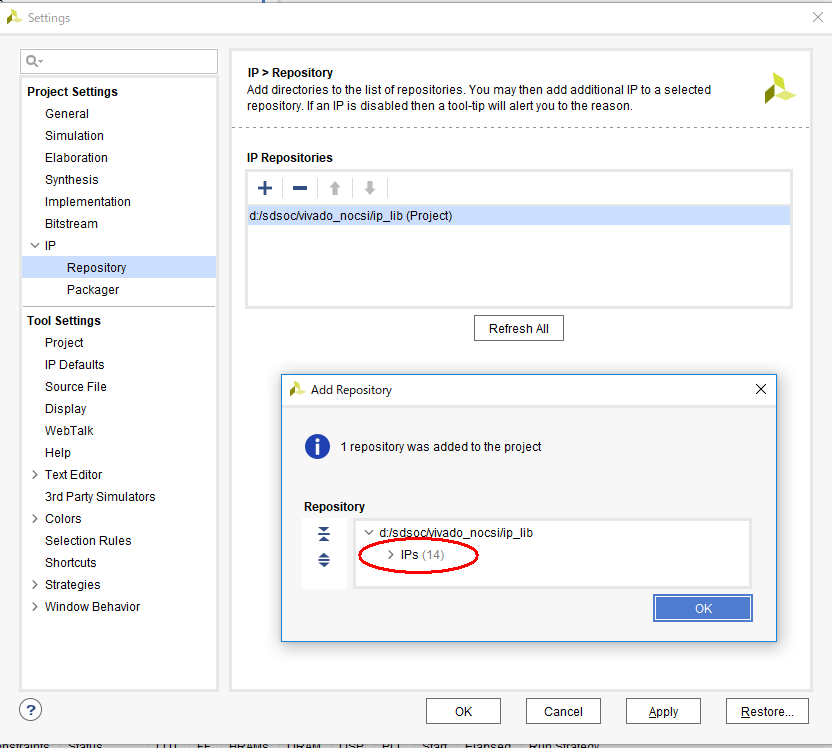

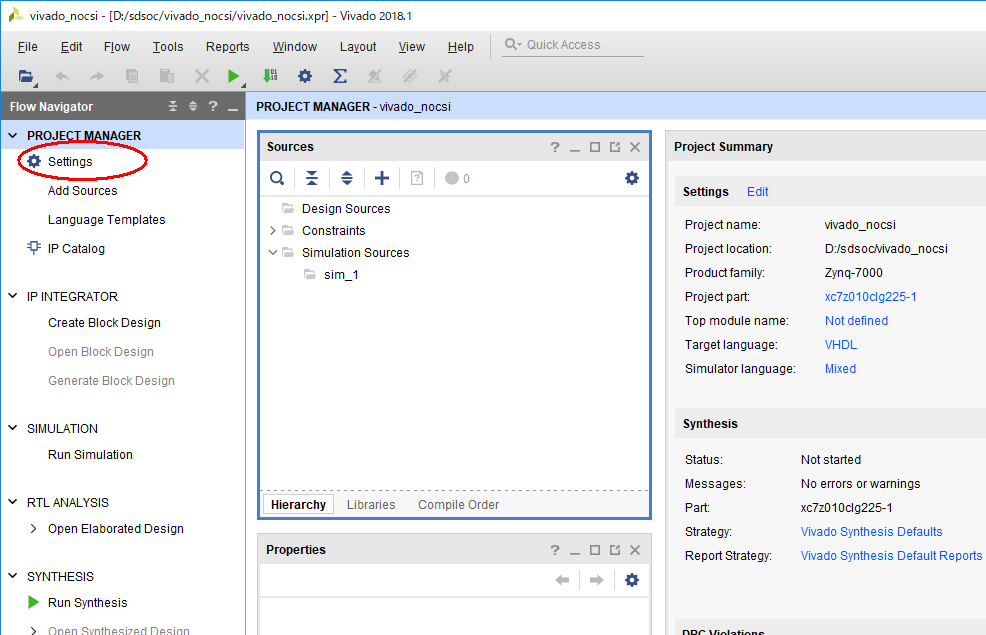

Vivadoのプロジェクトが作成され、メイン画面が表示されるので、Settingsをクリックします。

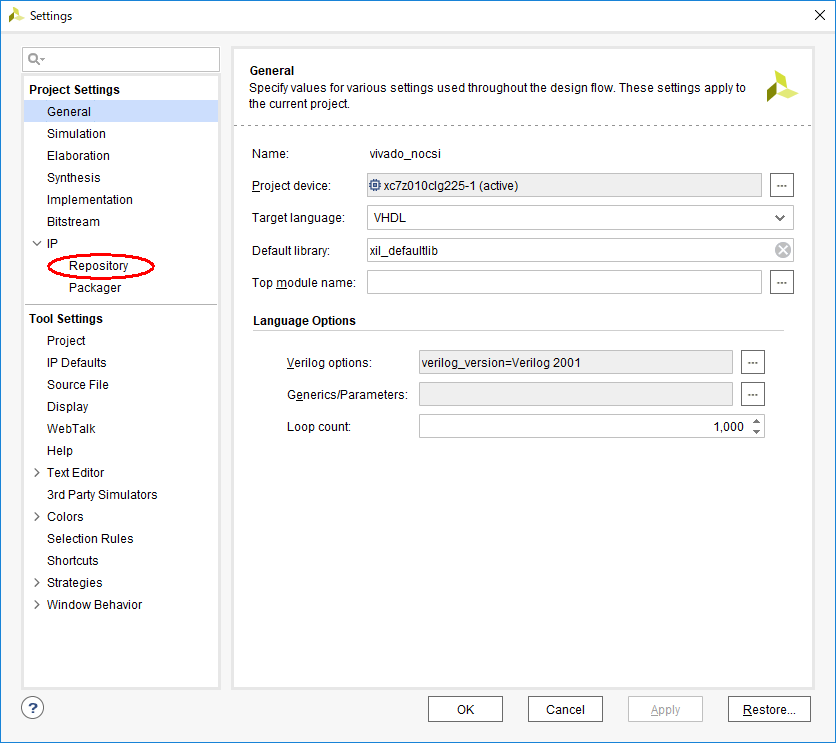

Settingsダイアログが表示されるので、Repositoryを選択します。

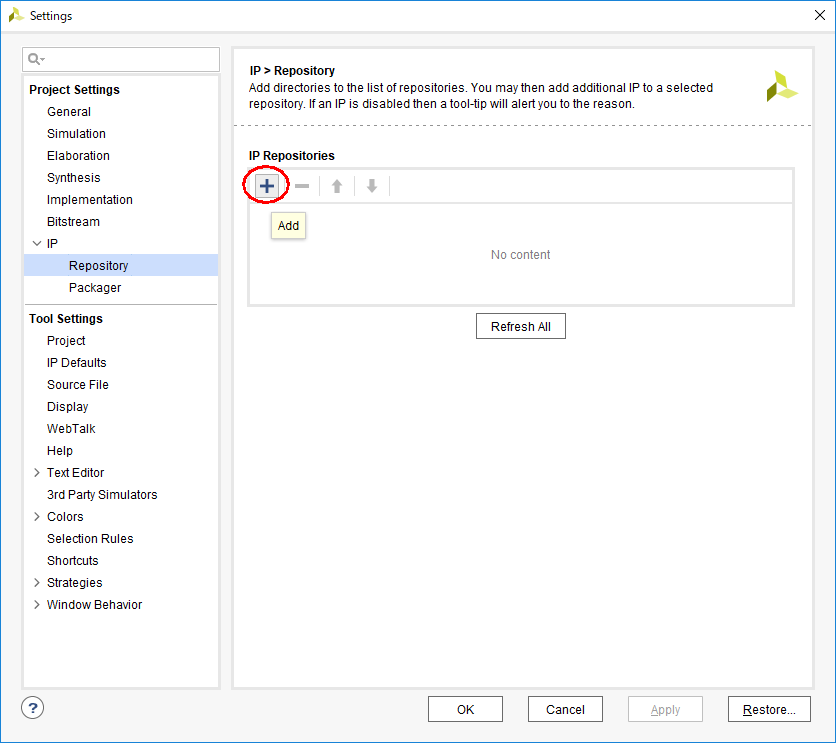

Addを押します。

フォルダ名を聞かれるので、d:\sdsoc\vivado_nocsi\ip_libを選択します。14個のIPsと表示されるはずです。

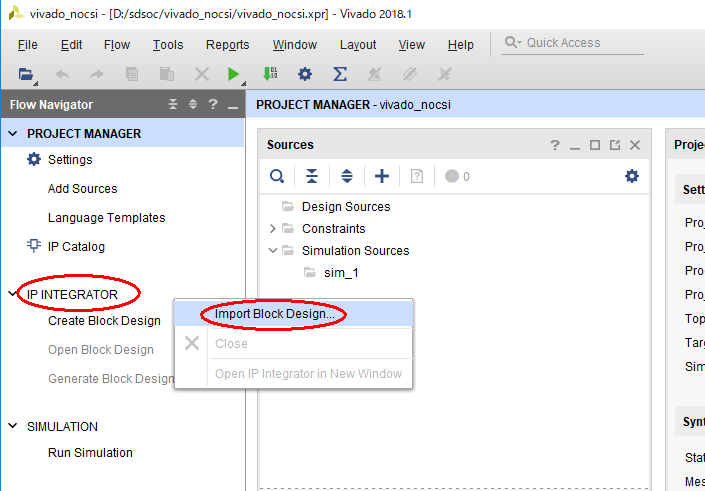

Block Designの読み込み

Vivadoのメイン画面に戻るので、IP INTEGRATORのところで右クリックし、Import Block Designを実行します。

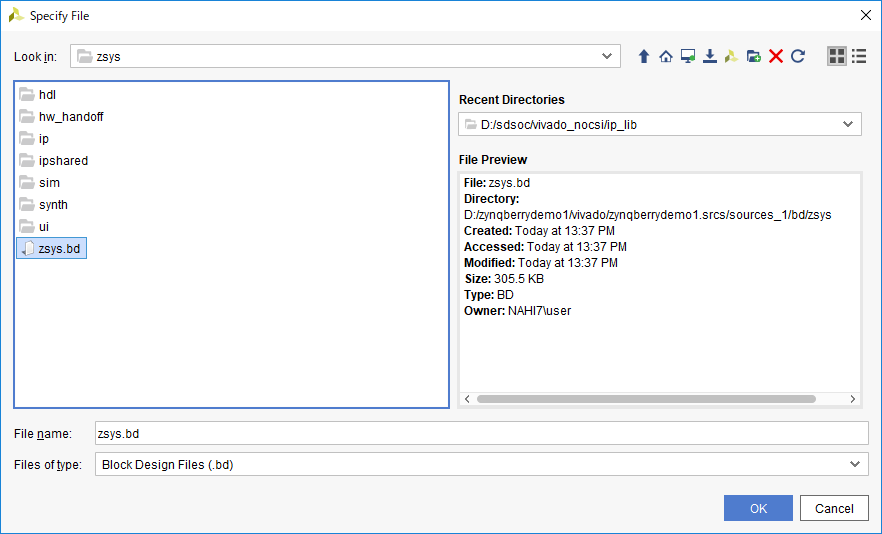

前のページで作成したbdファイルを指定します。

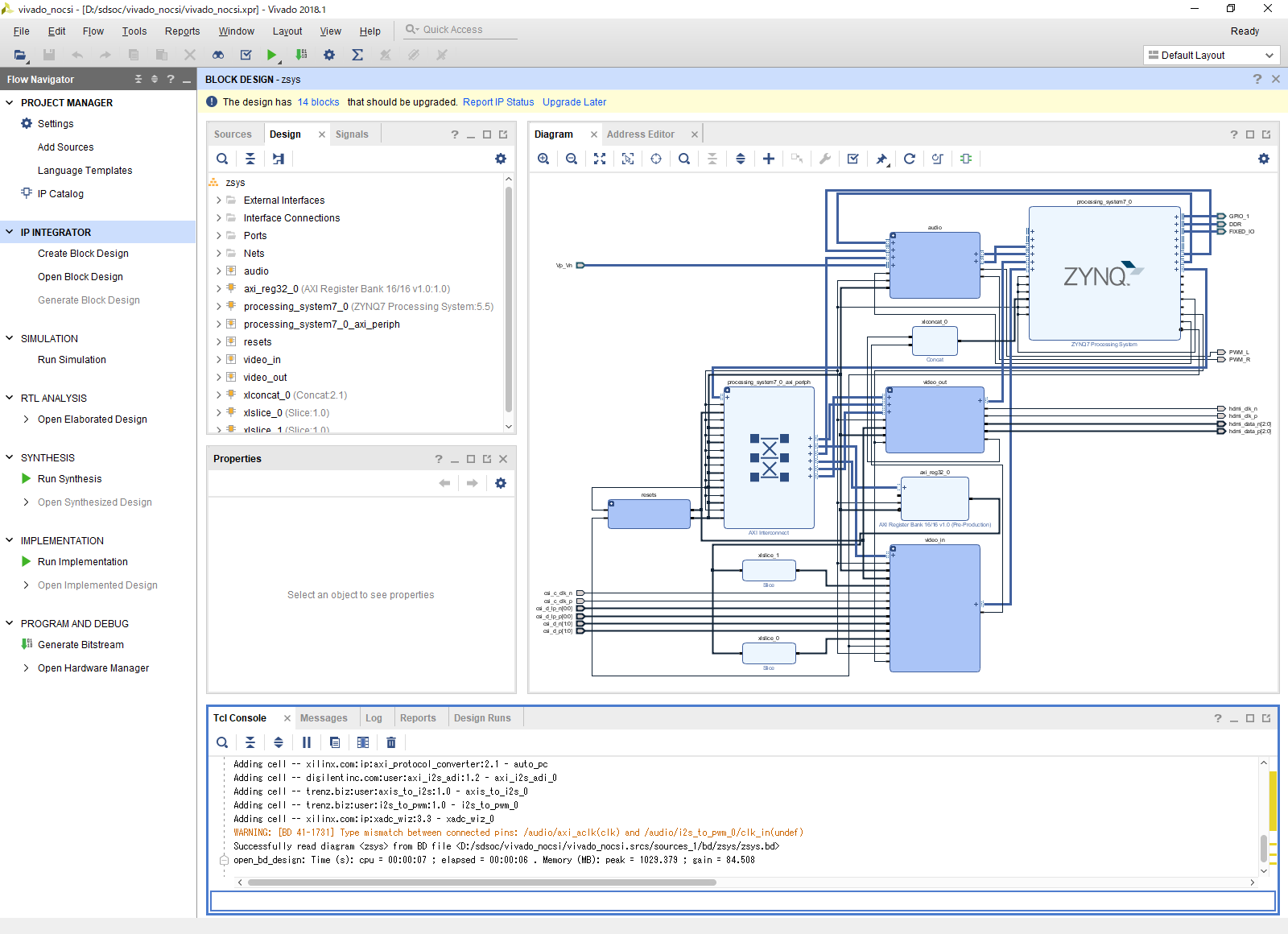

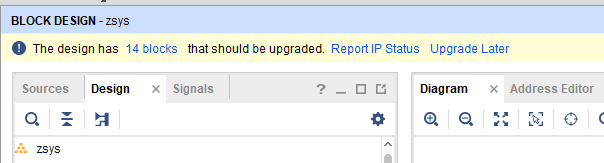

Vivado 2017.4で生成されたBlock Designがインポートされます。IPレポジトリの設定が正しく行われていれば、特にエラーなく進むはずです。

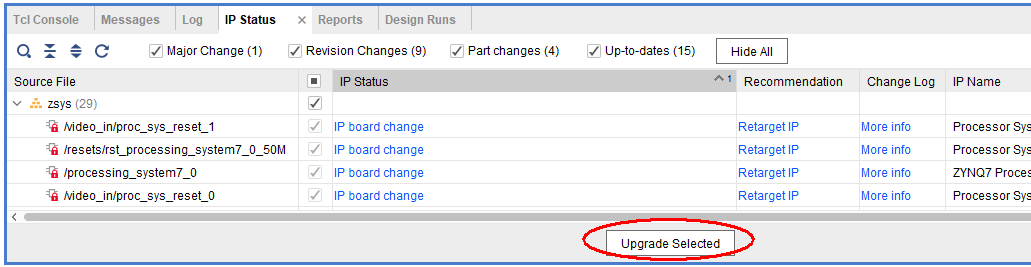

Report IP Statusをクリックし、

Upgrade Selectedを実行します。

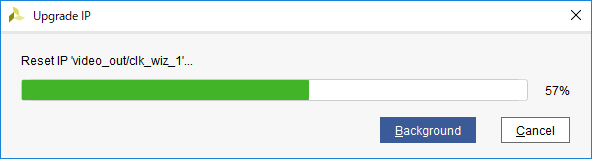

何かを処理しているようなダイアログが出て、

十数秒程度で

と表示されるはずです。