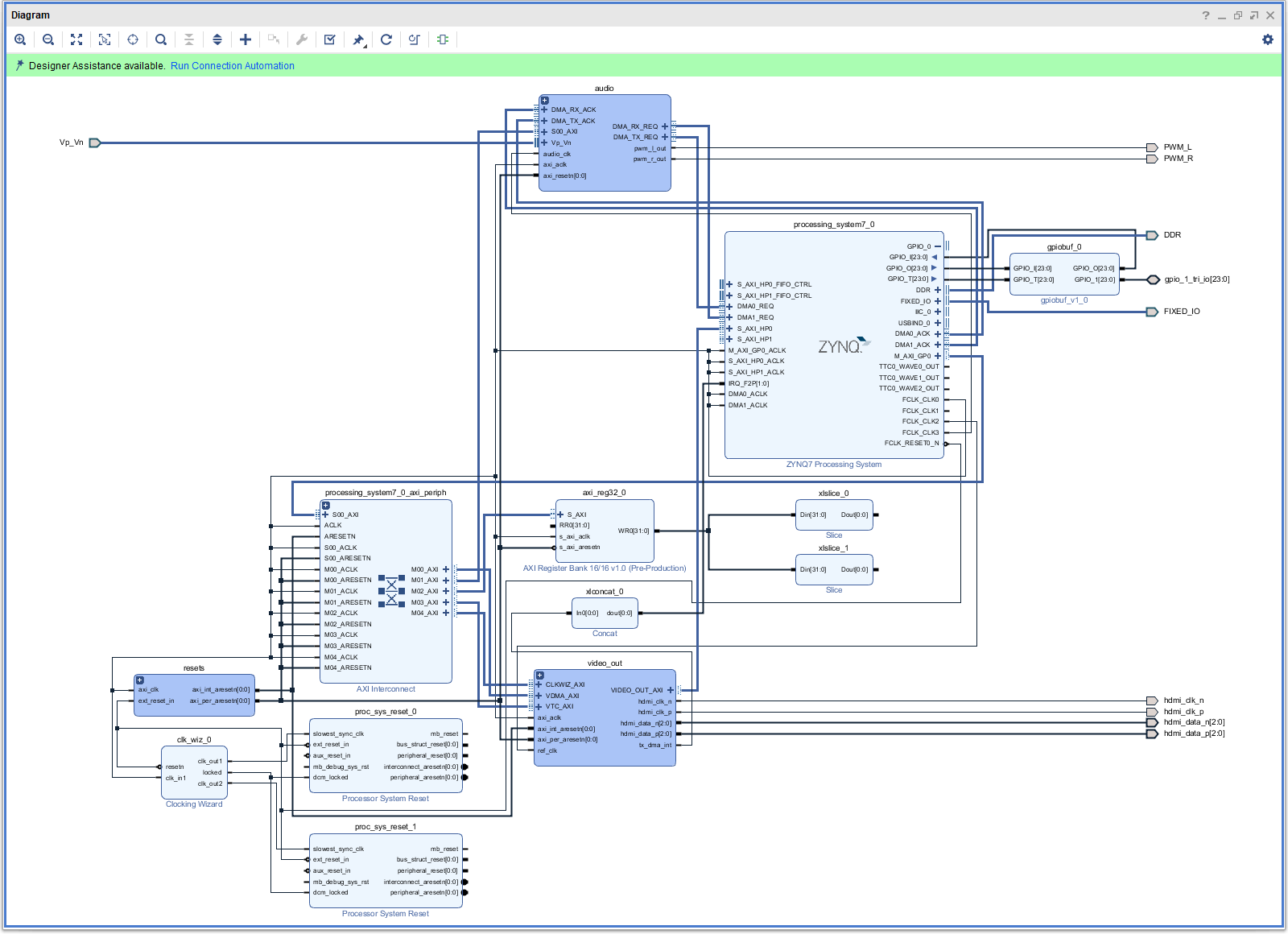

SDSoC用回路の追加

エラーのでないZynqberrydemo回路ができたら、SDSoCで使うプラットフォーム化する手順を説明します。

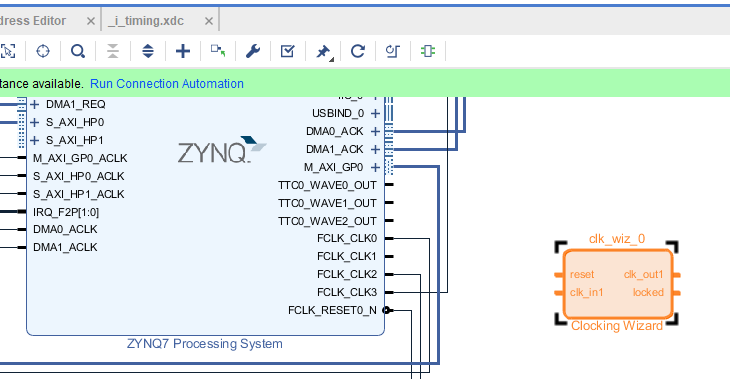

クロックモジュールの追加

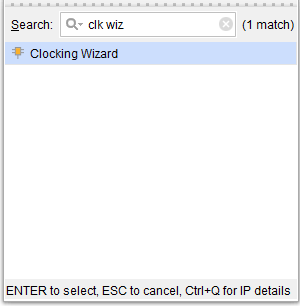

Open Block Designで開いたら、+ボタンを押して、検索ダイアログにclk wizを入力します。

Clocking Wizardがヒットするので、これを追加します。

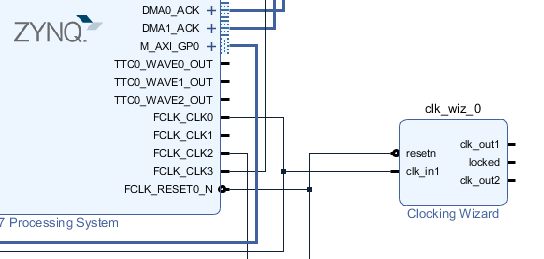

追加されたクロックモジュールをPS7の右のあたりにもってきて、ダブルクリックして開きます。

Output Clocksのタブを開き、clk_out1を100MHzに、clk_out2を200MHzにし、Reset TypeをLowにします。

これでOKを押します。

ZYNQのPS7のFCLK_CLK0をclk_wizのclk_in1に接続し、FCLK_RESET0_Nをresetnに接続します。

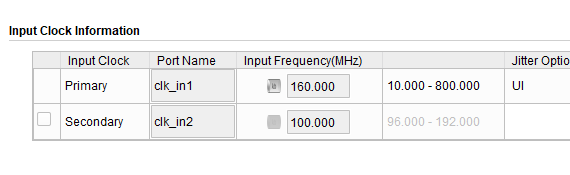

Validate Designした後でclk_wizを開いてみると、Input Clockの周波数が160MHzに変わっています。Vivadoではクロック周波数などはAutoにしておけば、Validate Designを行うことで伝搬させることができます。

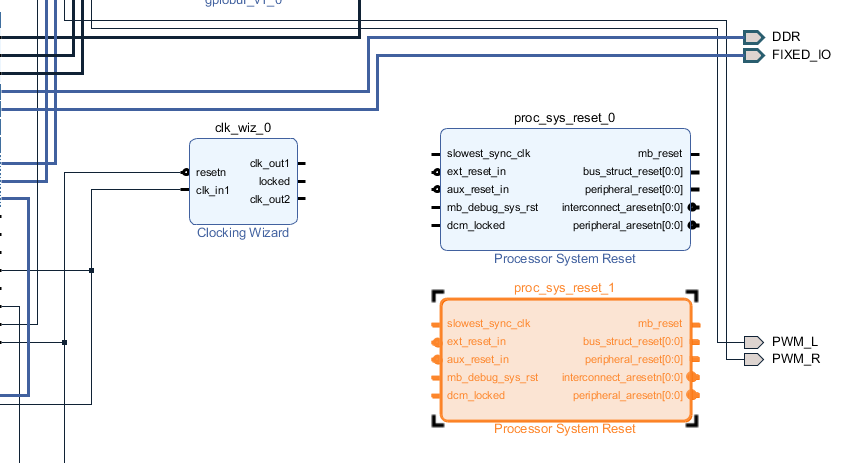

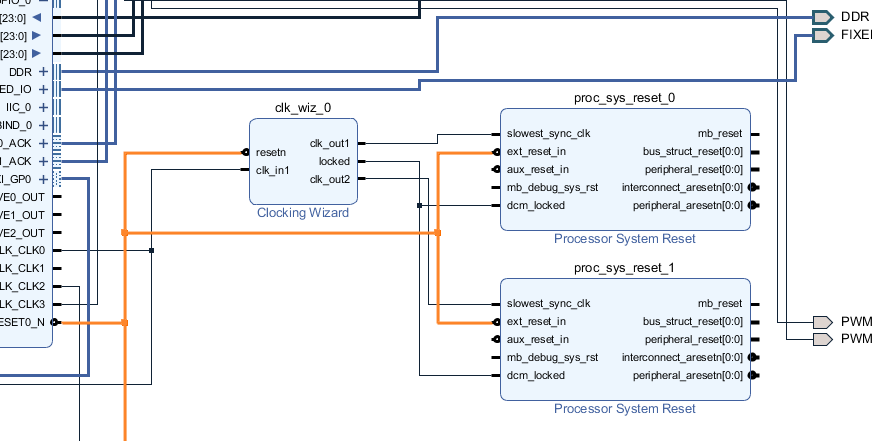

リセットモジュールの追加

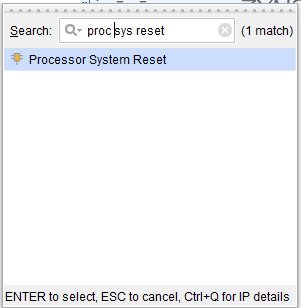

Block Designで+ボタンを押して、検索ダイアログにproc sys resetと入力します。

Processor System Resetがヒットするので、これを2個追加します。(上で作ったクロックの個数追加する)

- clk_out1をproc_sys_reset_0のslowest_sync_clkに

- clk_out2をproc_sys_reset_1のslowest_sync_clkに

- lockedをproc_sys_reset_0と1のdcm_lockedに

- PS7のFCLK_RESET0_Nををproc_sys_reset_0と1のext_reset_inに

それぞれつなぎます。

proc_sys_resetの出力はどこにもつなげずに、オープンにしておきます。

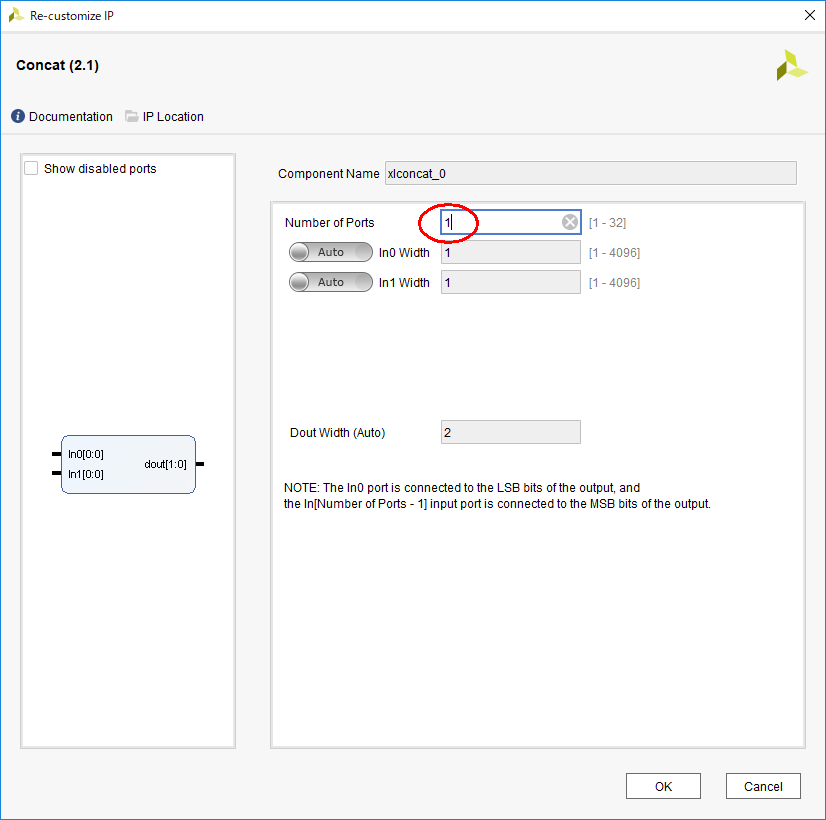

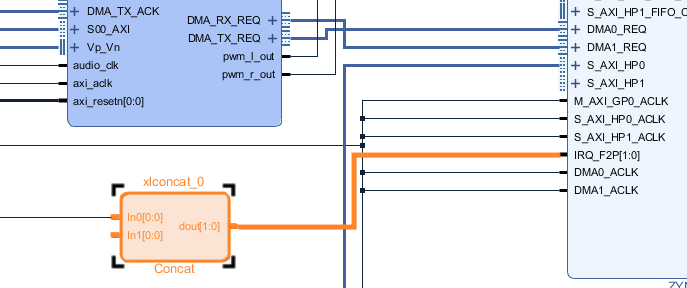

割り込み用concatの修正

SDSoCデザインでは割り込み信号をまとめるためのconcatを必要としますが、Zynqberryデザインではすでに存在しているので、これを利用します。

このxlconcat_0をダブルクリックして、設定を開きます。

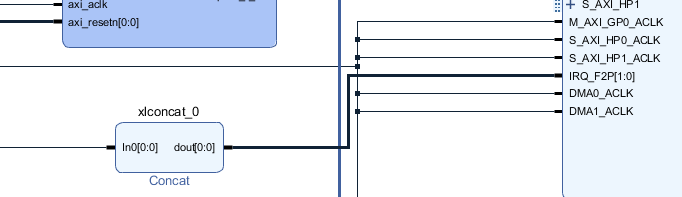

Number of Portsを1にして、OKを押します。

割り込み用concatのサイズが縮小します。

デザインの完成

これでようやくプラットフォームデザインの完成です。

念のため、いちど、Generate BitStreamを行ってみてください。